# iPod Authentication Coprocessor 2.0C Specification

Release R1

2011-06-22

#### Ś

Apple Inc. © 2011 Apple Inc. All rights reserved.

No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, mechanical, electronic, photocopying, recording, or otherwise, without prior written permission of Apple Inc., with the following exceptions: Any person is hereby authorized to store documentation on a single computer for personal use only and to print copies of documentation for personal use provided that the documentation contains Apple's copyright notice.

The Apple logo is a trademark of Apple Inc.

Use of the "keyboard" Apple logo (Option-Shift-K) for commercial purposes without the prior written consent of Apple may constitute trademark infringement and unfair competition in violation of federal and state laws.

No licenses, express or implied, are granted with respect to any of the technology described in this document. Apple retains all intellectual property rights associated with the technology described in this document. This document is intended to assist application developers to develop applications only for Apple-labeled computers.

Every effort has been made to ensure that the information in this document is accurate. Apple is not responsible for typographical errors.

Apple Inc. 1 Infinite Loop Cupertino, CA 95014 408-996-1010

Apple, the Apple logo, iPhone, iPod, and Pages are trademarks of Apple Inc., registered in the United States and other countries.

iPad is a trademark of Apple Inc.

IOS is a trademark or registered trademark of Cisco in the U.S. and other countries and is used under license.

Simultaneously published in the United States and Canada.

Even though Apple has reviewed this document, APPLE MAKES NO WARRANTY OR REPRESENTATION, EITHER EXPRESS OR IMPLIED, WITH RESPECT TO THIS DOCUMENT, ITS QUALITY, ACCURACY, MERCHANTABILITY, OR FITNESS FOR A PARTICULAR PURPOSE. AS A RESULT, THIS DOCUMENT IS PROVIDED "AS IS," AND YOU, THE READER, ARE ASSUMING THE ENTIRE RISK AS TO ITS QUALITY AND ACCURACY.

IN NO EVENT WILL APPLE BE LIABLE FOR DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES RESULTING FROM ANY DEFECT OR INACCURACY IN THIS DOCUMENT, even if advised of the possibility of such damages.

THE WARRANTY AND REMEDIES SET FORTH ABOVE ARE EXCLUSIVE AND IN LIEU OF ALL OTHERS, ORAL OR WRITTEN, EXPRESS OR IMPLIED. No Apple dealer, agent, or employee is authorized to make any modification, extension, or addition to this warranty.

Some states do not allow the exclusion or limitation of implied warranties or liability for incidental or consequential damages, so the above limitation or exclusion may not apply to you. This warranty gives you specific legal rights, and you may also have other rights which vary from state to state.

#### Contents

#### Introduction 7 Chapter 1 Overview 7 Authentication Protocol 7 Terminology Used in This Document 8 General Specification Terms 9 Related Documents 9 Signal Descriptions and Reference Circuit 11 Chapter 2 **CP** Signals and Pinouts 11 Address Selection 12 Reference Circuit 12 Chapter 3 Hardware Configuration and Interface 13 System Voltage 13 Startup of the I2C Interface 13 Starting Up the CP by Turning Power On 13 Starting Up the CP by Warm Reset 14 Communication Process 15 Low-Power Sleep Mode 16 Chapter 4 **Coprocessor Registers** 17 Register Addresses 17 **Register Descriptions** 19 Device Version 19 Firmware Version 19 Authentication Protocol Major and Minor Versions 20 Device ID 20 Error Code 20 Authentication Control and Status 21 Signature Data Length 22 Signature Data 22 Challenge Data Length 23 Challenge Data 23 Accessory Certificate Data Length 23 Accessory Certificate Data 23 Self-Test Control and Status 23 System Event Counter 24

|            | Apple Device Certificate Data 25                                                                                                                                                                                                                           |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 5  | Authentication Data Flows 27                                                                                                                                                                                                                               |

| (88)       | Apple Device Authentication of Accessory 27                                                                                                                                                                                                                |

|            | Accessory Authentication of the Apple Device 28                                                                                                                                                                                                            |

| 10         | 126 Communication Destand 21                                                                                                                                                                                                                               |

| Chapter 6  | 12C Communication Protocol 31                                                                                                                                                                                                                              |

|            | Slave Selection and Reset 31                                                                                                                                                                                                                               |

|            |                                                                                                                                                                                                                                                            |

|            |                                                                                                                                                                                                                                                            |

|            | Reading non-the coprocessor 52                                                                                                                                                                                                                             |

| Chapter 7  | CP Device Characteristics 33                                                                                                                                                                                                                               |

|            | Apple Device Authentication of Accessory 27<br>Accessory Authentication of the Apple Device 28<br>I2C Communication Protocol 31<br>Slave Selection and Reset 31<br>Coprocessor Busy 31<br>Writing to the Coprocessor 31<br>Reading from the Coprocessor 32 |

|            |                                                                                                                                                                                                                                                            |

|            |                                                                                                                                                                                                                                                            |

|            | I2C Interface Characteristics 34                                                                                                                                                                                                                           |

|            |                                                                                                                                                                                                                                                            |

|            | Timing Characteristics 35                                                                                                                                                                                                                                  |

| Annendix A | Coprocessor 2 0B to 2 0C Migration Guide 37                                                                                                                                                                                                                |

|            |                                                                                                                                                                                                                                                            |

|            |                                                                                                                                                                                                                                                            |

|            |                                                                                                                                                                                                                                                            |

|            |                                                                                                                                                                                                                                                            |

|            |                                                                                                                                                                                                                                                            |

|            |                                                                                                                                                                                                                                                            |

|            |                                                                                                                                                                                                                                                            |

|            | System Event Counter Must Be Zero Before Power-Down 38                                                                                                                                                                                                     |

|            | Document Revision History 39                                                                                                                                                                                                                               |

|            |                                                                                                                                                                                                                                                            |

|            |                                                                                                                                                                                                                                                            |

|            |                                                                                                                                                                                                                                                            |

|            |                                                                                                                                                                                                                                                            |

|            |                                                                                                                                                                                                                                                            |

|            |                                                                                                                                                                                                                                                            |

|            |                                                                                                                                                                                                                                                            |

|            |                                                                                                                                                                                                                                                            |

|            |                                                                                                                                                                                                                                                            |

|            |                                                                                                                                                                                                                                                            |

| Fig           | jures and         | Tables                                                                          |

|---------------|-------------------|---------------------------------------------------------------------------------|

|               |                   |                                                                                 |

| $(\beta   g)$ |                   |                                                                                 |

| Chapter 1     | Introductio       | on /                                                                            |

| 50            | Table 1-1         | Document-specific terminology 8                                                 |

|               |                   |                                                                                 |

| Chapter 2     | Signal Des        | criptions and Reference Circuit 11                                              |

|               | Figure 2-1        | CP chip pinouts, top view 11                                                    |

|               | Figure 2-2        | Reference circuit for CP 12                                                     |

|               | Table 2-1         | CP signals 11                                                                   |

|               | Table 2-2         | Address selection signals 12                                                    |

|               |                   |                                                                                 |

| Chapter 3     | Hardware          | Configuration and Interface 13                                                  |

|               | Figure 3-1        | I <sup>2</sup> C interface startup timing 14                                    |

|               | Figure 3-2        | I <sup>2</sup> C interface warm reset timing 15                                 |

|               | Figure 3-3        | I <sup>2</sup> C slave write address 15                                         |

|               | Figure 3-4        | I <sup>2</sup> C slave read address 15                                          |

|               | $\langle \rangle$ | $((\bigcirc))$ $(\bigcirc)$                                                     |

| Chapter 4     | Coprocess         | or Registers 17                                                                 |

|               | Figure 4-1        | Authentication Control and Status register, read-only bits 21                   |

|               | Figure 4-2        | Authentication Control and Status register, write-only bits 21                  |

|               | Figure 4-3        | Self-test Control and Status register, write-only bits 23                       |

|               | Figure 4-4        | Self-test Control and Status register, read-only bits 24                        |

|               | Table 4-1         | iPod Authentication Coprocessor 2.0C register map 17                            |

|               | Table 4-2         | Error codes 20                                                                  |

|               | Table 4-3         | Authentication ERR_SET values 21                                                |

|               | Table 4-4         | Authentication PROC_RESULTS values 21                                           |

|               | Table 4-5         | Authentication PROC_CONTROL values 22                                           |

|               | Table 4-6         | Self-test PROC_CONTROL values 24                                                |

|               | Table 4-7         | Self-test result bits 24                                                        |

|               | A the surt is a   | tion Data Flaura 27                                                             |

| Chapter 5     | Authentica        | ation Data Flows 27                                                             |

|               | Table 5-1         | Sequence of interactions by which an Apple device authenticates an accessory 27 |

|               | Table 5-2         | Sequence of interactions by which an accessory authenticates an Apple device 28 |

|               |                   |                                                                                 |

#### Chapter 7 CP Device Characteristics 33

|        | Figure 7-1 | Authentication coprocessor 2.0C package 33                          |

|--------|------------|---------------------------------------------------------------------|

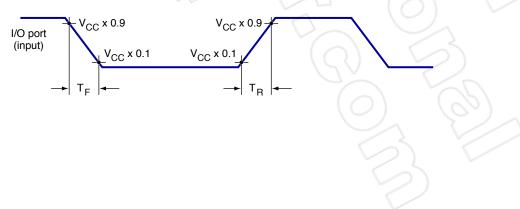

|        | Figure 7-2 | Typical I/O port input waveform 35                                  |

|        | Table 7-1  | Maximum electrical and temperature ranges 34                        |

| $\sim$ | Table 7-2  | Recommended operating conditions 34                                 |

|        | Table 7-3  | I <sup>2</sup> C interface ranges 34                                |

|        | Table 7-4  | Supply current into V <sub>CC</sub> , excluding external current 35 |

|        | Table 7-5  | Inputs 35                                                           |

|        | Table 7-6  | Outputs 35                                                          |

|        | Table 7-7  | Values for Figure 7-2 36                                            |

|        |            |                                                                     |

# Introduction

NOTICE OF PROPRIETARY PROPERTY: THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY PROPERTY OF APPLE INC. THE POSSESSOR AGREES TO THE FOLLOWING: (I) TO MAINTAIN THIS DOCUMENT IN CONFIDENCE, (II) NOT TO REPRODUCE OR COPY IT, (III) NOT TO REVEAL OR PUBLISH IT IN WHOLE OR IN PART, (IV) ALL RIGHTS RESERVED.

ACCESS TO THIS DOCUMENT AND THE INFORMATION CONTAINED THEREIN IS GOVERNED BY THE TERMS OF THE MFI LICENSE AGREEMENT AND/OR THE IPOD-IPHONE AIS EVALUATION AGREEMENT. ALL OTHER USE SHALL BE AT APPLE'S SOLE DISCRETION.

**Note:** This document uses the term "Apple device" to refer generically to iPods, iPhones, and iPads, all of which support the iPod Accessory Protocol (iAP) interface. Among these products, those that also run iOS (Apple's mobile operating system) are referred to as "iOS devices." Specifications in this document that are designated for iOS devices apply only to those products. Specifications designated for iPods apply only to Apple devices that are not iOS devices.

#### **Overview**

An Apple device verifies whether a third-party accessory attached to it is authorized for use with the Apple device by issuing an authentication challenge to the accessory. The accessory must respond to the Apple device's challenge, and it can do so only with the assistance of an **iPod Authentication Coprocessor** (CP) chip located in the accessory. Conversely, the accessory can use its CP chip to authenticate the iPod. Certain control and reporting functions of the Apple device are made available externally only after it has authenticated an attached accessory as being authorized.

Earlier versions of the iPod Authentication Coprocessor (1.0, 2.0A, and 2.0B) were implemented in QFN-40, QFN-20, and SOP-8 packages. The current version, 2.0C, is supplied in a smaller and more efficient PG-USON-8-1 package. This document describes the configuration, usage, and specifications of Apple's iPod Authentication Coprocessor 2.0C.

#### **Authentication Protocol**

The authentication protocol supported by the iPod Authentication Coprocessor 2.0C is based on standard X.509 version 3 certification. Each certificate is generated and signed by a recognized certificate authority and has a unique serial number. Information about the X.509 standard can be found at the IETF website http://tools.ietf.org/html/3280.

For information about the iAP General lingo commands required to perform authentication using the iPod Authentication Coprocessor 2.0C, see Apple's *MFi Accessory Firmware Specification*.

The iPod Authentication Coprocessor 2.0C supports iAP General lingo commands 0x14 through 0x1F, providing five authentication-related services:

#### For Apple device authentication of the accessory:

- **Certificate delivery:** To initiate authenticatication of the accessory that contains it, the CP supplies an X.509 digital certificate for public key verification by the attached Apple device.

- Signature generation: To complete authentication of the accessory that contains it, the CP generates a valid digital signature in response to a challenge from an attached Apple device. This signature authorizes the Apple device to respond to messages and commands from the accessory.

#### For accessory authentication of the Apple device:

- Apple device certificate validation: To initiate the authentication of an Apple device attached to an accessory, the CP verifies that the X.509 certificate supplied by Apple device has been signed by the proper certificate authority.

- Challenge generation: To continue the authentication of an Apple device attached to an accessory, the accessory's CP can generate a challenge to be sent to the Apple device.

- **Signature verification:** To complete the authentication of an Apple device attached to the accessory, the CP can verify the signature returned by the Apple device in response to the previous challenge.

## Terminology Used in This Document

Certain technical terms specific to this document are defined in Table 1-1.

| Term                       | Definition                                                                                                                                                                                                                                                                            |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Accessory controller       | The microcontroller in an accessory responsible for implementing application-specific logic.                                                                                                                                                                                          |

| Authentication coprocessor | A device in an accessory controller that provides Apple device-related digital signature creation and verification services.                                                                                                                                                          |

| Challenge                  | A random number sent via iAP from an Apple device to an accessory controller, or vice versa. The device being challenged must perform a digital signature computation on the offered challenge and return the resulting digital signature to the challenging device for verification. |

| Digital signature          | The result obtained by performing a digital signing process on an offered challenge.                                                                                                                                                                                                  |

| iAP                        | iPod Accessory Protocol. See Apple's MFi Accessory Firmware Specification.                                                                                                                                                                                                            |

| l²C bus                    | A 2-wire serial bus designed by Philips to allow easy communication between components that reside on the same circuit board. The I <sup>2</sup> C specification is located at http://www.semiconductors.philips.com/ acrobat_download/litera-ture/9398/39340011.pdf.                 |

| Table 1-1 | Document-specific terminology |

|-----------|-------------------------------|

|           |                               |

Introduction

| Term                | Definition                                                                                                                                                                                                                                                                                                          |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| X.509 certification | A standard defined by the International Telecommunication Union (ITU) that<br>governs the format of certificates used for authentication and sender identity<br>verification in public-key cryptography. X.509 certificates contain the public keys<br>used in the Apple device's accessory authentication process. |

## General Specification Terms

Parts of this document contain specification requirements that are incorporated by reference into legal agreements between Apple Inc. and its licensees. The use of the words "must," "should," and "may" in these specifications have the following meanings:

- "Must" means that the specification is an absolute requirement.

- "Must not" means that the specification is an absolute prohibition.

- "Should" means that there may be valid reasons in particular circumstances to ignore the specification, but their full implications must be understood and carefully weighed before choosing to do so.

- "Should not" means that there may be valid reasons in particular circumstances that make the specified action or feature acceptable, but their full implications must be understood and carefully weighed before choosing to include it.

- "May" means that the indicated action or feature does not contravene this specification.

# **Related Documents**

For further information about authenticating Apple devices and their attached accessories, see Apple's *MFi* Accessory Firmware Specification and *MFi* Accessory Hardware Specification.

Introduction

# Signal Descriptions and Reference Circuit

This chapter defines the pinouts, signals, and reference circuitry of the iPod Authentication Coprocessor 2.0C.

# **CP** Signals and Pinouts

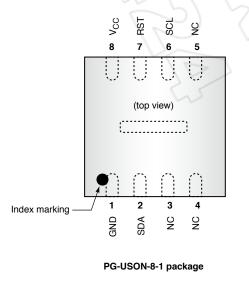

The 2.0C CP chip signal descriptions are given in Table 2-1 and its pinouts are shown in Figure 2-1.

| Signal name     | Pin | I/O    | Description                                                                        |

|-----------------|-----|--------|------------------------------------------------------------------------------------|

| GND             | 1   | /      | Supply voltage, negative terminal                                                  |

| SDA             | 2   | I/O    | I²C data                                                                           |

| NC              | 3-5 |        | Must not be connected                                                              |

| SCL             | 6   | L      | l²C clock                                                                          |

| RST             | 7   | D)     | At reset: selects I <sup>2</sup> C slave address. During operation: CP warm reset. |

| V <sub>CC</sub> | 8   | $\leq$ | Supply voltage, positive terminal                                                  |

| Table 2-1 | CP signals |

|-----------|------------|

|-----------|------------|

Figure 2-1 CP chip pinouts, top view

The thermal pad on the bottom of the CP may be left unconnected or optionally connected to GND.

# **Address Selection**

After power-up or in response to a warm reset, the state of RST is used to select the CP's I<sup>2</sup>C slave addresses, as shown in Table 2-2.

Table 2-2

Address selection signals

| RST state | I <sup>2</sup> C add | dresses |

|-----------|----------------------|---------|

|           | Write                | Read    |

| 0         | 0x20                 | 0x21    |

| 1         | 0x22                 | 0x23    |

See "Communication Process" (page 15) for the interface requirements of the CP's I<sup>2</sup>C slave communication transport.

# **Reference Circuit**

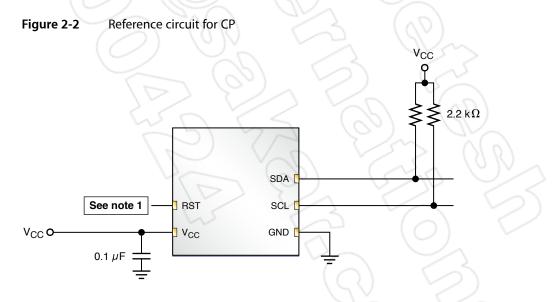

The reference circuit for I<sup>2</sup>C operation of the CP is shown in Figure 2-2.

Note 1: If the CP's warm reset function is not needed, RST can be tied to either V<sub>CC</sub> or GND, depending on which of the addressing modes shown in Table 2-2 is used. If the warm reset function is needed, RST should be connected to a general-purpose I/O line on the accessory's controller. For further details, see Starting Up the CP by Warm Reset (page 14).

# Hardware Configuration and Interface

This chapter describes the operating modes of the iPod Authentication Coprocessor 2.0C and the ways that it interacts with other circuitry.

### System Voltage

The 2.0C CP may be used either in an accessory powered by an attached Apple device or in an accessory that has its own power source.

#### Startup of the I<sup>2</sup>C Interface

The CP's I<sup>2</sup>C communication interface can be started up either by supplying power to the V<sub>CC</sub> line or by performing a warm reset on the RST line. The accessory actions required for these two procedures are specified in the next sections.

#### Starting Up the CP by Turning Power On

To activate the  $I^2C$  interface by supplying power to the  $V_{CC}$  line, the accessory must perform the following startup procedure. This procedure is required both to support address selection by means of the RST line and to support the option of a warm reset later.

- The V<sub>CC</sub> line must be supplied with power and the SDA and SCL lines must be set high during the entire procedure.

- The RST line, used to select addressing as described in Address Selection (page 12), must be kept either low or high during the entire procedure. If the RST line is kept low during the procedure, the accessory must set it high not earlier than 10 ms after the V<sub>CC</sub> line goes high but before the first data transmission occurs.

- The first data transmission may start not earlier than 10 ms after the V<sub>CC</sub> line goes high. If the RST line has been kept low and the accessory might need to perform a warm reset of the CP chip later, the accessory must set the RST line high not earlier that 1 ms after the start of the first data transmission (t<sub>H.RST</sub> interval in Figure 3-1 (page 14)). If the option of a warm reset later is not needed, the accessory may tie RST directly to either V<sub>CC</sub> or GND.

Figure 3-1 (page 14) diagrams the timing of the I<sup>2</sup>C interface when it is started up by turning power on.

#### Hardware Configuration and Interface

In this diagram,  $t_{STARTUP} \ge 10$  ms and  $t_{H.RST} \ge 1$  ms. The rise time of  $t_R$  and the fall time of  $t_F$  are both < 1 µs from 10% to 90% of the signal amplitude, and  $t_{POWER-UP} < 200$  µs from VCC = 0.4 V until VCC = 90% of the target supply voltage.

#### Starting Up the CP by Warm Reset

To reset the I<sup>2</sup>C interface through the RST line, after activating it through power-up as specified in Starting Up the CP by Turning Power On (page 13), the accessory must perform the following procedure:

- The V<sub>CC</sub> line must be supplied with power during the entire procedure.

- The terminal must halt I<sup>2</sup>C communication, and the SDA and SCL lines must be set high before the RST line is set low.

- The RST line must be set low and kept low for at least 10 µs. Not later than 1 ms after the falling edge of the RST signal, the accessory must finish its I<sup>2</sup>C address selection by either keeping RST low or driving RST high. If the RST line is kept low during the warm reset, the accessory must set it high not earlier than 10 ms after the V<sub>CC</sub> line goes high but before the first data transmission occurs.

- The first data transmission may start not earlier than 10 ms after the falling edge of the RST signal. If the RST line has been kept low during the warm reset, the accessory must set it high not earlier that 1 ms after the start of the first data transmission (t<sub>H.RST</sub> interval in Figure 3-2 (page 15)).

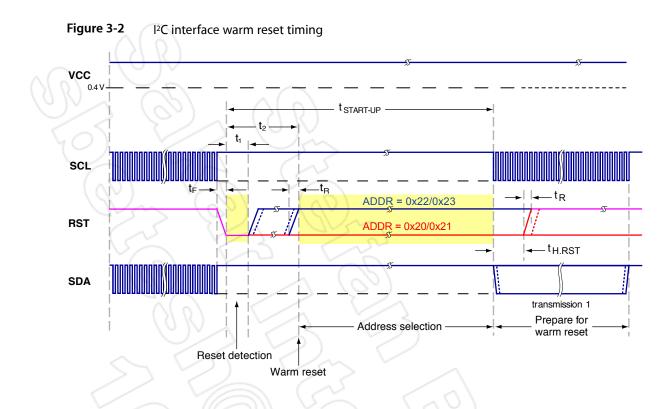

Figure 3-2 (page 15) diagrams the timing of the I<sup>2</sup>C interface when it is reset by software toggling the RST line without a power off/on cycle.

#### Hardware Configuration and Interface

In this diagram,  $t_{\text{STARTUP}} \ge 10 \text{ ms}$ ,  $t_{\text{H.RST}} \ge 1 \text{ ms}$ ,  $t_1 > 10 \text{ }\mu\text{s}$ , and  $t_2 = 3 \text{ ms}$ . The rise time of  $t_R$  and the fall time of  $t_F$  are both  $< 1 \text{ }\mu\text{s}$  from 10% to 90% of the signal amplitude.

### **Communication Process**

When the CP is addressed using I<sup>2</sup>C, it acts as a standard 7-bit I<sup>2</sup>C slave. The I<sup>2</sup>C slave address is configured upon reset and is based on the RST input. The I<sup>2</sup>C effective slave address for writing is shown in Figure 3-3 and the corresponding read address in Figure 3-4.

| Figure 3-3 | I <sup>2</sup> C slave | write addres | s  |    | 5  |     |      |

|------------|------------------------|--------------|----|----|----|-----|------|

| A6         | A5                     | A4           | A3 | A2 | A1 | AO  | R/nW |

| 0          | 0                      | 1            | 0  | 0  | 0  | RST | 0    |

| Figure 3-4 | I <sup>2</sup> C slave | read address | 5  |    |    | N   |      |

| A6         | A5                     | A4           | A3 | A2 | A1 | A0  | R/nW |

| 0          | 0                      | 1            | 0  | 0  | 0  | RST | 1    |

|            |                        |              |    |    | 5  |     |      |

In I<sup>2</sup>C mode, the CP has both a write address and a read address, as is typical for an I<sup>2</sup>C device. The I<sup>2</sup>C write address of the CP consists of the seven bits [A6:A0] followed by 0 for the R/nW bit. The I<sup>2</sup>C read address of the CP consists of the seven bits [A6:A0] followed by 1 for the R/nW bit. If the RST input is connected to ground, the write and read addresses of the CP are 0x20 and 0x21 respectively; if it is pulled high, the write and read addresses of the CP are 0x23.

# Low-Power Sleep Mode

The 2.0C CP conserves power by entering a Sleep mode. It enters this mode automatically and cannot be forced to it externally. When in Sleep mode, the CP automatically wakes in response to any I<sup>2</sup>C communications sent to its address.

# **Coprocessor Registers**

Registers within the iPod Authentication Coprocessor 2.0C (CP) are accessed via I<sup>2</sup>C transport, as described in Communication Process (page 15). This chapter specifies the CP's register addressing details and telegram formats.

# **Register Addresses**

Registers and their addresses in the CP are listed in Table 4-1. Each register is discussed in the sections that follow.

**Note:** Registers in the same block with consecutive addresses may be read from sequentially in increasing numerical order, except as noted in the last column of Table 4-1. Registers must not be written to sequentially except as noted. Multibyte numeric values are stored in big-endian order; for example, the first byte in a two-byte register is the MSB of the stored value and the second byte is its LSB.

| Register<br>address | Block | Register name                            | Length<br>in bytes | Contents after<br>reset | Access                         | Notes |

|---------------------|-------|------------------------------------------|--------------------|-------------------------|--------------------------------|-------|

| 0x00                | 0     | Device Version                           | $\gamma$           | 0x05                    | Read-only                      |       |

| 0x01                | 0     | Firmware Version                         | 1                  | 0x01                    | Read-only                      |       |

| 0x02                | 0     | Authentication Protocol Major<br>Version | 1                  | 0x02                    | Read-only                      |       |

| 0x03                | 0     | Authentication Protocol Minor<br>Version | 1                  | 0x00                    | Read-only                      |       |

| 0x04                | 0     | Device ID                                | 4                  | 0x00000200              | Read-only                      |       |

| 0x05                | 0     | Error Code                               | 16                 | 0x00                    | Read-only<br>(cleared on read) | 1     |

|                     |       |                                          | 7                  | 5 5                     | 50                             |       |

| 0x10                | 1     | Authentication Control and Status        | 1                  | 0x00                    | Read/write                     |       |

| 0x11                | 1     | Signature Data Length                    | 2                  | 128                     | Read/write                     | 2     |

| 0x12                | 1     | Signature Data                           | 128                | Undefined               | Read/write                     |       |

Table 4-1

iPod Authentication Coprocessor 2.0C register map

**Coprocessor Registers**

| Register<br>address | Block | Register name                           | Length<br>in bytes | Contents after<br>reset | Access     | N |

|---------------------|-------|-----------------------------------------|--------------------|-------------------------|------------|---|

| $V \subset$         | Zr    |                                         |                    |                         |            |   |

| 0x20                | 200   | Challenge Data Length                   | 2                  | 20                      | Read/write | 2 |

| 0x21                | 2     | Challenge Data                          | 128                | Undefined               | Read/write |   |

|                     |       | CA CA                                   |                    |                         |            |   |

| 0x30                | 3     | Accessory Certificate Data<br>Length    | 2                  | ≤1280                   | Read-only  |   |

| 0x31                | 3     | Accessory Certificate Data<br>(Page 1)  | 128                | Certificate             | Read-only  |   |

| 0x32                | 3     | Accessory Certificate Data<br>(Page 2)  | 128                | Certificate             | Read-only  |   |

| 0x33                | 3     | Accessory Certificate Data<br>(Page 3)  | 128                | Certificate             | Read-only  |   |

| 0x34                | 3     | Accessory Certificate Data<br>(Page 4)  | 128                | Certificate             | Read-only  |   |

| 0x35                | 3     | Accessory Certificate Data<br>(Page 5)  | 128                | Certificate             | Read-only  |   |

| 0x36                | 3     | Accessory Certificate Data<br>(Page 6)  | 128                | Certificate             | Read-only  |   |

| 0x37                | 3     | Accessory Certificate Data<br>(Page 7)  | 128                | Certificate             | Read-only  |   |

| 0x38                | 3     | Accessory Certificate Data<br>(Page 8)  | 128                | Certificate             | Read-only  |   |

| 0x39                | 3     | Accessory Certificate Data<br>(Page 9)  | 128                | Certificate             | Read-only  |   |

| 0x3A                | 3     | Accessory Certificate Data<br>(Page 10) | 128                | Certificate             | Read-only  |   |

|                     |       |                                         | 16                 |                         | 3          |   |

| 0x40                | 4     | Self-test Control and Status            | 15                 | 0x00                    | Read/write |   |

| 0x41-0x4C           | 4     | Reserved                                |                    | O) (                    | 201        |   |

| 0x4D                | 1     | System Event Counter (SEC)              | 1                  | Undefined               | Read-only  |   |

**Coprocessor Registers**

| Register<br>address | - / / / / |                                           | Length<br>in bytes | Contents after<br>reset | Access     | Notes |

|---------------------|-----------|-------------------------------------------|--------------------|-------------------------|------------|-------|

| 0x50                | 5         | Apple Device Certificate Data<br>Length   | 2                  | 0x0000                  | Read/write |       |

| 0x51                | 5         | Apple Device Certificate Data<br>(Page 1) | 128                | Undefined               | Read/write |       |

| 0x52                | 5         | Apple Device Certificate Data<br>(Page 2) | 128                | Undefined               | Read/write |       |

| 0x53                | 5         | Apple Device Certificate Data<br>(Page 3) | 128                | Undefined               | Read/write |       |

| 0x54                | 50        | Apple Device Certificate Data<br>(Page 4) | 128                | Undefined               | Read/write |       |

| 0x55                | 5         | Apple Device Certificate Data<br>(Page 5) | 128                | Undefined               | Read/write |       |

| 0x56                | 5         | Apple Device Certificate Data<br>(Page 6) | 128                | Undefined               | Read/write |       |

| 0x57                | 5         | Apple Device Certificate Data<br>(Page 7) | 128                | Undefined               | Read/write |       |

| 0x58                | 5         | Apple Device Certificate Data<br>(Page 8) | 128                | Undefined               | Read/write |       |

**Note 1:** Register 0x05 can be read sequentially only as part of a sequence that begins with a register in the range 0x00–0x04, in which case the read operation does not clear it.

Note 2: Registers 0x11 and 0x20 may each be written sequentially with registers 0x12 and 0x21, respectively.

# **Register Descriptions**

This section describes the ways that the CP registers listed in Table 4-1 are used.

#### **Device Version**

The Device Version read-only register contains the version number of the coprocessor device. The current Authentication 2.0C coprocessor is designated as device version 0x05.

#### **Firmware Version**

The Firmware Version read-only register contains the version number of the coprocessor firmware. Firmware version numbers advance by whole integers.

#### Authentication Protocol Major and Minor Versions

The Authentication Protocol Major Version and Authentication Protocol Minor Version read-only registers provide the version number of the authentication protocol that the CP supports. This information is accessed by the iAP command RetDevAuthenticationInfo during accessory authentication.

## Device ID

The Device ID read-only register identifies the accessory and is accessed by the iAP command SetFIDTokenValues during accessory identification.

### **Error Code**

The Error Code read-only register stores the most recent communication or authentication process error code generated since the register was last cleared. The error code register is cleared after it is read. The possible error codes are listed in Table 4-2.

If a single communication operation happens to produce multiple errors (for example, by writing an invalid signature length during a multiregister write that also attempts to continue past the end of the corresponding block) then only the highest-numbered error code is stored.

| 10        |                                                      |

|-----------|------------------------------------------------------|

| Code      | Description                                          |

| 0x00      | No error                                             |

| 0x01      | Invalid register for read                            |

| 0x02      | Invalid register for write                           |

| 0x03      | Invalid signature length                             |

| 0x04      | Invalid challenge length                             |

| 0x05      | Invalid certificate length                           |

| 0x06      | Internal process error during signature generation   |

| 0x07      | Internal process error during challenge generation   |

| 0x08      | Internal process error during signature verification |

| 0x09      | Internal process error during certificate validation |

| 0x0A      | Invalid process control                              |

| 0x0B      | Process control out of sequence                      |

| 0x0C-0xFF | Reserved                                             |

|           |                                                      |

| Table 4-2 | Error codes |  |

|-----------|-------------|--|

|           |             |  |

#### Authentication Control and Status

The Authentication Control and Status read/write register provides control and status information for the CP's authentication processes.

When read from, the Authentication Control and Status register provides the status of the most recently requested CP process, as shown in Figure 4-1 and Tables 4-3 and 4-4.

| Figure 4-1 | Auther | Authentication Control and Status register, read-only bits |   |   |   |   |   |

|------------|--------|------------------------------------------------------------|---|---|---|---|---|

|            | 6      | 5                                                          | 4 | 3 | 2 | 1 | 0 |

| ERR_SET    | 2      | PROC_RESULT                                                | s | 0 | 0 | 0 | 0 |

Table 4-3 Authentication ERR\_SET values

| Value | Description                                                                                                                                                                                                                                                    |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The Error Code register does not contain a code generated by the most recent command execution.<br>However, it may still contain the most recent error code (greater than 0x00) generated by an earlier<br>command.                                            |

| 1     | The Error Code register contains the most recent process or communication error. Both this bit and the Error Code register contents are cleared after the Error Code register is next read. This bit is also cleared after every successful command execution. |

#### Authentication PROC\_RESULTS values Table 4-4

| Value | Description                                        |

|-------|----------------------------------------------------|

| 0     | Most recent process did not produce valid results. |

| 1     | Accessory signature successfully generated.        |

| 2     | Challenge successfully generated.                  |

| 3     | Apple device signature successfully verified.      |

| 4     | Apple device certificate successfully validated.   |

| 5-7   | Reserved.                                          |

When written to, the Authentication Control and Status register controls the start of CP processes, as shown in Figure 4-2 and Table 4-5 (page 22).

| Figure 4-2 | Authentication Control and Status register, write-only bits |

|------------|-------------------------------------------------------------|

|------------|-------------------------------------------------------------|

| _ | 7 | 6 | 5 | 4 | 3 | 2   | 1 3     | 0   |

|---|---|---|---|---|---|-----|---------|-----|

|   | 0 | 0 | 0 | 0 | 0 | PRC | C_CONTF | ROL |

**Coprocessor Registers**

Note: Attempts to write to other bits are ignored.

Table 4-5

Authentication PROC\_CONTROL values

| Value | Description                              | Notes                                                                                                                                       |

|-------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | No operation                             | This control does nothing and always reports success (ERR_SET = 0; PROC_RESULTS = 0).                                                       |

| 10    | Start new signature-generation process   |                                                                                                                                             |

| 2     | Start new challenge-generation process   | The length of the challenge to be generated is defined by<br>the Challenge Data Length register and ranges from 1 to<br>128 bytes.          |

| 3     | Start new signature-verification process | $(\mathcal{O}_{\mathcal{O}})$                                                                                                               |

| 4     | Start new certificate-validation process | Do not attempt to read the accessory certificate after<br>writing the Apple device certificate but before validating<br>it by this control. |

| 5     | No operation                             | This control does nothing and always reports success (ERR_SET = 0; PROC_RESULTS = 0).                                                       |

| 6-7   | Reserved.                                | 2 102                                                                                                                                       |

#### Signature Data Length

The Signature Data Length read/write register holds the length in bytes of the results of the most recent signature-generation process (if the Apple device is authenticating an accessory) or signature-verification process (if the accessory is authenticating the Apple device).

Before a signature-generation process begins, this register should contain 0x80, the maximum allowable signature length. After completion of the signature-generation process, the CP updates this register to contain the actual length of the generated signature. This updated value should be read in order to determine how much of the Signature Data register contains valid signature bytes.

Before a signature-verification process begins, this register should hold the actual length of the signature being verified.

#### Signature Data

In the case of a signature generation process, the Signature Data register holds the newly-generated data. In the case of a signature verification process, it holds the signature to be verified.

### Challenge Data Length

The Challenge Data Length read/write register holds the length, in bytes, of the current challenge. This challenge may either be written into the CP, during Apple device authentication of an accessory, or generated by the CP during accessory authentication of an Apple device.

Before starting a signature-generation process on the current challenge during Apple device authentication of an accessory, this register must contain the length of the challenge.

Before starting a new challenge-generation process during accessory authentication of an Apple device, this register should contain the requested challenge length. The length must be in the range is 1 to 128 bytes; writing any other value will cause an error.

The required length of an authentication challenge is 20 bytes.

### Challenge Data

The Challenge Data register holds the current challenge data. This data is either written into the CP or generated by the CP depending on the specific operation. The number of bytes used or generated is determined by the value of the Challenge Length Data register.

### Accessory Certificate Data Length

The Accessory Certificate Data Length read-only register holds the length of the X.509 certificate that the Apple device uses to authenticate an accessory. The length of a certificate varies but is always less than or equal to 1280 bytes. This length limit may not hold for future versions of the authentication protocol.

#### Accessory Certificate Data

The Accessory Certificate Data read-only register holds the PKCS#7-wrapped X.509 certificate that the Apple device uses to authenticate an accessory. The Accessory Certificate may be read from the coprocessor in 128-byte pages starting at any Accessory Certificate Data Page address, or it may be read in a continuous stream starting at Page 1. Since the length of the Accessory Certificate varies, fewer than all of the pages may be used. The Accessory Certificate Data Length value can be read to determine which Accessory Certificate Data Pages contain the certificate data.

#### Self-Test Control and Status

The Self-test Control and Status read/write register provides access to the built-in self-test functions of the coprocessor. When it is set to a value of 1, the Self-test Control and Status register initiates a self-test process, as shown in Figure 4-3 and Table 4-6 (page 24).

Figure 4-3 Self-test Control and Status register, write-only bits

| 7 | 6 | 5 | 4 | 3 | 2      | 1 0     |

|---|---|---|---|---|--------|---------|

| 0 | 0 | 0 | 0 | 0 | PROC_0 | CONTROL |

2-7

Reserved

**Coprocessor Registers**

Note: Attempts to write to other bits are ignored.

Table 4-6

Self-test PROC\_CONTROL values

Value

Test process to be run

0

None

1

Run X.509 certificate and private key tests

When read from, bits 7–4 of the Self-test Control and Status register report the results of the X.509 certificate and private key tests, as shown in Figure 4-4 and Table 4-7 (page 24). The CP detects a read cycle and resets the Control and Status register to 0x00 after it; hence bits 7–4 must all be retrieved in one operation.

| Figur | <b>e 4-4</b> Self-tes | t Control and Sta | atus reg | jister, read-only | v bits                    |               |          |

|-------|-----------------------|-------------------|----------|-------------------|---------------------------|---------------|----------|

|       | 7 6                   | 5                 | 4        | 3                 | 2                         | 1             | 0        |

|       | Self-Te               | est results       |          | 0                 | 0                         | 0             | 0        |

| Table | e 4-7 Self-test       | result bits       | 5        | aD                | [00]                      |               |          |

| Bit   | Test                  | No.               |          | Bit val           | ue                        |               |          |

|       | $(\mathcal{O}$        | 0                 |          |                   | B                         | m             |          |

| 7     | X.509 certificate     | Certificate not   | found    | Certificate fou   | und in memo               | ory (see note | e below) |

| 6     | Private key           | Private key not   | found    | Private key fo    | und in mem                | ory (see not  | e below) |

| 5-4   | Reserved              | 551               | 5        | J (               | 37)                       | NY.           |          |

|       | 1                     |                   |          | 0                 | $\langle \rangle \rangle$ |               | 01       |

**Note:** The X.509 and private key tests only verify that these elements are present in Flash memory; no authentication is performed.

#### System Event Counter

The System Event Counter (SEC) is a non-volatile register that holds the current value of the CP's event counter. The event counter automatically decrements one count per second while the CP is powered, stopping at 0. If the accessory controls power to the CP, it must wait until the SEC has decremented to 0 before removing power.

## Apple Device Certificate Data Length

The Apple Device Certificate Data Length register holds the length of the X.509 certificate supplied by the attached Apple device. An accessory uses this certificate to authenticate an Apple device in both the certificate validation and signature verification processes. The length of an Apple device certificate varies but is always less than or equal to 1024 bytes. This length limit may not hold for future versions of the authentication protocol.

Writing a value in a range greater than 0 and less than or equal to 1024 will cause the CP to validate the data contained in the iPod Certificate Data registers. If the CP invalidates the iPod Certificate Data, it sets this register to 0.

## Apple Device Certificate Data

The Apple Device Certificate Data register holds the X.509 Certificate that an accessory uses to authenticate an Apple device in both the certificate validation and signature verification processes. The Apple Device Certificate may be written to the coprocessor in 128-byte pages starting at any Apple Device Certificate Data Page address, but it may not be written in a multipage stream. Since the length of the Apple Device Certificate varies, not all of the pages need to be used. The Apple Device Certificate Data Length value determines which Apple Device Certificate Data Pages contain valid certificate data.

CHAPTER 4 Coprocessor Registers

# **Authentication Data Flows**

Authentication involves communication between the accessory controller (AC), the Authentication Coprocessor (CP) in the accessory, and the Apple device attached to the accessory.

Communication between the accessory controller and the CP takes place via the I<sup>2</sup>C transport link described in Communication Process (page 15). Communication between the accessory controller and the Apple device takes place via the iPod Accessory Protocol. See Apple's *MFi Accessory Firmware Specification* for full details.

This chapter summarizes the kinds of information that pass between the AC, the CP, and the attached Apple device (Dev).

# Apple Device Authentication of Accessory

The sequence of interactions by which an Apple device authenticates an accessory is shown in Table 5-1 (page 27). At the beginning of this process the accessory controller is granted access by the Apple device to the iAP lingo or lingoes it requests; however, if the process does not finish successfully that access is terminated.

| Command or action                                  | Direction | Comments                                                                                                                                                                                    |  |  |

|----------------------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Read Authentication Protocol Version and Device ID | CP -> AC  | Accessory controller reads authentication protocol version and device ID from CP                                                                                                            |  |  |

| StartIDPS (iAP)                                    | AC -> Dev | The accessory controller initiates and completes the                                                                                                                                        |  |  |

| SetFIDTokenValues (iAP)                            | AC -> Dev | Identify Device Preferences and Settings (IDPS) process.<br>It sends the Apple device a set of ID tokens, one of                                                                            |  |  |

| EndIDPS (iAP)                                      | AC -> Dev | which includes the device ID returned by the CP. See <i>MFi Accessory Firmware Specification</i> , Chapter 2 and Appendix A.                                                                |  |  |

| GetDevAuthenticationInfo(iAP)                      | Dev -> AC | The Apple device requests device authentication info                                                                                                                                        |  |  |

| Read Accessory Certificate Length and Data         | CP -> AC  | Accessory controller reads Accessory certificate from CP                                                                                                                                    |  |  |

| RetDevAuthenticationInfo (iAP)                     | AC -> Dev | Accessory controller returns information needed for<br>authentication process, using the authentication<br>protocol version number and X.509 certificate return<br>by the CP                |  |  |

| AckDevAuthenticationInfo (iAP)                     | Dev -> AC | The status of the authentication version comparison<br>is returned to the accessory controller. The returned<br>status includes information about the validity of the<br>X.509 certificate. |  |  |

Table 5-1

Sequence of interactions by which an Apple device authenticates an accessory

#### Authentication Data Flows

| Command or action                                 | Direction | Comments                                                                                                             |

|---------------------------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------|

| GetDevAuthenticationSignature (iAP)               | Dev -> AC | The Apple device sends accessory controller a challenge and requests that it provide corresponding digital signature |

| Write Challenge Length and Challenge<br>Data      | AC -> CP  | Accessory controller writes challenge into CP                                                                        |

| Write Authentication Control:<br>PROC_CONTROL = 1 | AC -> CP  | Accessory controller starts signature-generation process in CP                                                       |

| Wait for process completion                       | CP -> AC  | Accessory controller waits for CP to finish processing                                                               |

| Read Authentication Status                        | CP -> AC  | Accessory controller reads Authentication Status and checks PROC_RESULTS field                                       |

| Read Signature Data Length and Signature Data     | CP -> AC  | Accessory controller reads signature from CP                                                                         |

| RetDevAuthenticationSignature (iAP)               | AC -> Dev | Accessory controller returns signature to the Apple device                                                           |

| AckDevAuthenticationStatus<br>(iAP)               | Dev -> AC | Resulting success or failure of signature verification sent to accessory controller by the Apple device              |

# Accessory Authentication of the Apple Device

The sequence of interactions by which an accessory authenticates an Apple device is shown in Table 5-2.

Table 5-2

Sequence of interactions by which an accessory authenticates an Apple device

| Command or action                                                       | Direction           | Comments                                                                                                   |

|-------------------------------------------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------|

| Read Authentication Protocol<br>Version and Device ID                   | CP -> AC            | Accessory controller reads authentication protocol version and device ID from CP                           |

| The accessory controller performs t 5-1 (page 27).                      | he accessory iden   | tification and authentication processes listed in Table                                                    |

|                                                                         |                     | icates the accessory, must finish successfully before                                                      |

| the sequence by which the accesso                                       | ory authenticates t | the Apple device can continue.                                                                             |

| the sequence by which the accesso<br>GetiPodAuthenticationInfo<br>(iAP) | AC -> Dev           | the Apple device can continue.<br>Accessory controller requests Apple device<br>authentication information |

| GetiPodAuthenticationInfo                                               | •                   | Accessory controller requests Apple device                                                                 |

#### Authentication Data Flows

| Command or action                                 | Direction | Comments                                                                                                                                     |

|---------------------------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Write Authentication Control:<br>PROC_CONTROL = 4 | AC -> CP  | Accessory controller starts certificate validation process in CP                                                                             |

| Wait for process completion                       | CP -> AC  | Accessory controller waits for CP to finish processing                                                                                       |

| Read Authentication Status                        | CP -> AC  | Accessory controller reads Authentication Statu and checks PROC_RESULTS field                                                                |

| AckiPodAuthenticationInfo<br>(iAP)                | AC -> Dev | Results of the authentication information comparison are returned to the Apple device                                                        |

| Write Authentication Control:<br>PROC_CONTROL = 2 | AC -> CP  | Accessory controller starts challenge-generatio process in CP to calculate new challenge                                                     |

| Wait for process completion                       | CP -> AC  | Accessory controller waits for CP to finish processing                                                                                       |

| Read Authentication Status                        | CP -> AC  | Accessory controller reads the authentication status and checks PROC_RESULTS field                                                           |

| Read Challenge Length and<br>Challenge Data       | CP -> AC  | Accessory controller reads challenge from CP                                                                                                 |

| GetiPodAuthentication-<br>Signature (iAP)         | AC -> Dev | Accessory controller sends challenge to the<br>Apple device and requests that it calculate<br>digital signature                              |

| RetiPodAuthentication-<br>Signature <b>(iAP)</b>  | Dev -> AC | The Apple device returns a digital signature to the Accessory controller                                                                     |

| Write Signature Data Length and<br>Signature Data | AC -> CP  | Accessory controller writes digital signature int CP                                                                                         |

| Write Challenge Length and<br>Challenge           | AC -> CP  | Accessory controller writes challenge into CP (<br>needs to write this into the CP only if the<br>challenge has been changed in the meantime |

| Write Authentication Control:<br>PROC_CONTROL = 3 | AC -> CP  | Accessory controller starts signature-verificatio process in CP                                                                              |

| Wait for process completion                       | CP -> AC  | Accessory controller waits for CP to finish processing                                                                                       |

| Read Authentication Status                        | CP -> AC  | Accessory controller reads authentication statu<br>and checks PROC_RESULTS field                                                             |

| AckiPodAuthenticationStatus<br>(iAP)              | AC -> Dev | Signature verification status is returned to the Apple device.                                                                               |

#### **CHAPTER 5** Authentication Data Flows

# **I2C Communication Protocol**

The iPod Authentication Coprocessor (CP) supports the I<sup>2</sup>C communication protocol, acting as an I<sup>2</sup>C slave. Its SCL signal is the I<sup>2</sup>C clock line and is driven by the accessory controller. Its SDA signal is the I<sup>2</sup>C data line and is driven by whichever device is currently sending data.

Unlike the iPod Authentication Coprocessor version 2.0B, CP 2.0C does not perform clock synchronization by stretching SCL. It may, however, not-acknowledge (NACK) a requested register operation if busy, so the I<sup>2</sup>C master should expect retry operations as a normal part of CP 2.0C use.

The maximum supported I<sup>2</sup>C clock rate is 400 kHz.

#### **Slave Selection and Reset**

During reset, the RST signal must specify the CP's I<sup>2</sup>C slave address and must be held stable for at least 10 ms after power-up or reset, as described in "Communication Process" (page 15). As an I<sup>2</sup>C slave, the CP is then selected in-band via its I<sup>2</sup>C address. The least significant bit of the I<sup>2</sup>C slave address controls whether a write or a read operation is to be performed, as described in "Address Selection" (page 12).

#### **Coprocessor Busy**

When the CP is busy processing it is unable to handle incoming communication attempts. If the coprocessor does not ACK its slave address during an attempted I<sup>2</sup>C communication, then the coprocessor is busy. The accessory controller must repeatedly attempt communication until the coprocessor sends an ACK after receiving its slave address.

## Writing to the Coprocessor

To write data to the coprocessor, follow these steps:

- 1. Send the I<sup>2</sup>C start sequence.

- 2. Send the I<sup>2</sup>C write address of the CP.

- 3. Check for an ACK from the slave; if a NACK is received, wait 500 µs and then loop back to Step 1.

- 4. Send the register address at which to begin writing.

- 5. Send the data bytes.

**I2C Communication Protocol**

6. Send the I<sup>2</sup>C stop sequence.

# Reading from the Coprocessor

To read data from the coprocessor, follow these steps:

- 1. Send the I<sup>2</sup>C start sequence.

- 2. Send the I<sup>2</sup>C write address of the CP.

- 3. Check for an ACK from the slave; if a NACK is received, wait 500 µs and then loop back to Step 1.

- 4. Send the register address at which to begin reading.

- 5. Optional: send the I<sup>2</sup>C stop sequence.

- 6. Send the I<sup>2</sup>C start sequence.

- 7. Send the I<sup>2</sup>C read address of the CP.

- 8. Check for an ACK from the slave; if a NACK is received, wait 500 µs and then loop back to Step 6.

- 9. Read the data bytes.

- **10.** Send the I<sup>2</sup>C stop sequence.

Any additional reads after an I<sup>2</sup>C read stop sequence continue with the byte following the previous byte read until an invalid register address or an end of block is reached, at which point the slave returns 0xFF in response to all further reads.

# **CP Device Characteristics**

This chapter provides technical details and tolerances for the Apple iPod Authentication Coprocessor 2.0C (CP) chip.

## **Physical Configuration**

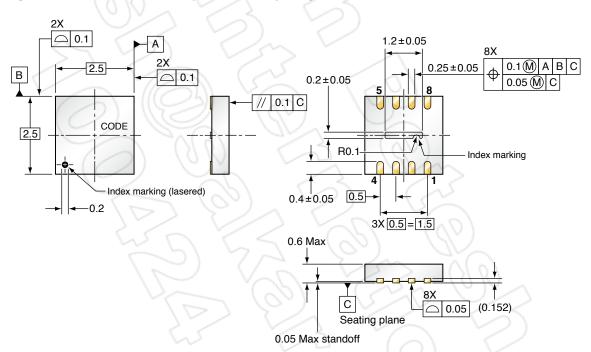

Figure 7-1 shows the CP package's layout, pin locations, and dimensional tolerances.

Figure 7-1 Authentication coprocessor 2.0C package

## **Maximum Environmental Conditions**

Table 7-1 (page 34) lists the CP's absolute maximum electrical and free-air temperature ranges. Stresses to the CP chip beyond the ranges listed in Table 7-1 may cause permanent damage. Exposure to either end of any range for extended periods may affect device reliability.

| Condition                                        | Maximum range                     |

|--------------------------------------------------|-----------------------------------|

| Voltage applied at $V_{CC}$ relative to $V_{SS}$ | –0.3 V to +7.0 V                  |

| Voltage applied to any pin                       | –0.3 V to V <sub>CC</sub> + 0.3 V |

| Storage temperature                              | –40 °C to +125 °C                 |

#### Table 7-1Maximum electrical and temperature ranges

# **Recommended Operating Conditions**

The CP is available only in a standard temperature range configuration. Internal sensors may force it to its reset state if any of the conditions listed in Table 7-2 are exceeded. Attempting to operate the CP in this state is not recommended and may lead to device failure or unreliability.

| Table 7-2 | Recommended | operating conditions |

|-----------|-------------|----------------------|

|-----------|-------------|----------------------|

| Condition                               | Minimum | Maximum | Unit |

|-----------------------------------------|---------|---------|------|

| Operating free-air temperature          | -25     | +85     | °C   |

| Supply voltage during program execution | 1.62    | 5.5     | v    |

## **I2C Interface Characteristics**

Table 7-3 specifies the limits of the I<sup>2</sup>C interface between the CP and other components.

| Table 7-3 | I <sup>2</sup> C interface ranges |

|-----------|-----------------------------------|

|-----------|-----------------------------------|

| Parameter                                            | Minimum | Maximum | Unit |

|------------------------------------------------------|---------|---------|------|

| SCL clock frequency (f <sub>SCL</sub> )              | 10      | 400     | kHz  |

| External bus capacitance to ground (C <sub>b</sub> ) |         | 100     | pF   |

## **DC Electrical Characteristics**

Tables 7-4 through 7-6 (page 35) show the DC electrical characteristics of the CP chip over its recommended voltage and temperature ranges. Unless otherwise specified in these tables,  $V_{CC} = 1.62$  to 5.5 V and  $T_A = -25$  °C to +85 °C.

#### Table 7-4 Supply current into V<sub>CC</sub>, excluding external current

| Parameter                                                      | Test conditions        | Minimum | Typical | Maximum | Unit |